文章资讯

AMD Zen5锐龙9000内核布局解密:512位浮点单元大变

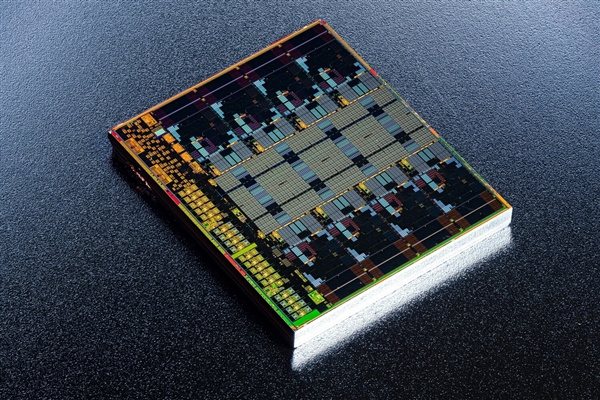

10月7日消息,Nemez、Fitzchens Fitz、HighYieldYT等多位大神共同完成了Zen5架构锐龙9000系列的内核解密,包括高清照片、模块分布图。

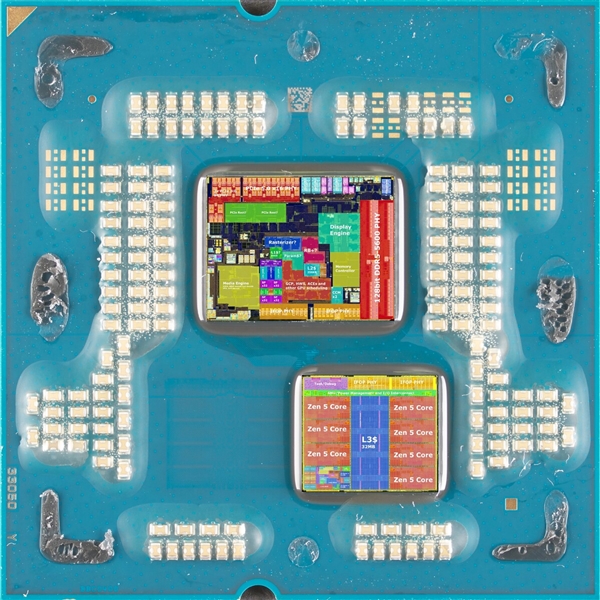

锐龙9000系列延续了chiplet布局,包括一颗或两颗CCD、一颗IOD。

其中,CCD升级架构的同时,制造工艺也从N5 5nm升级为N4P 4nm,IOD则和锐龙7000系列上的完全一样,工艺也还是N6 6nm。

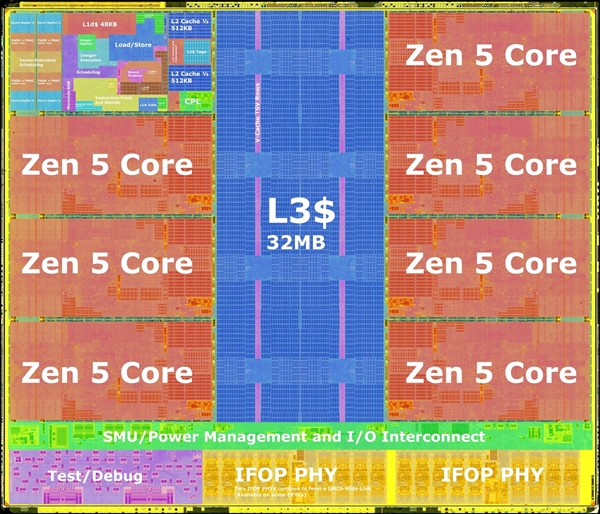

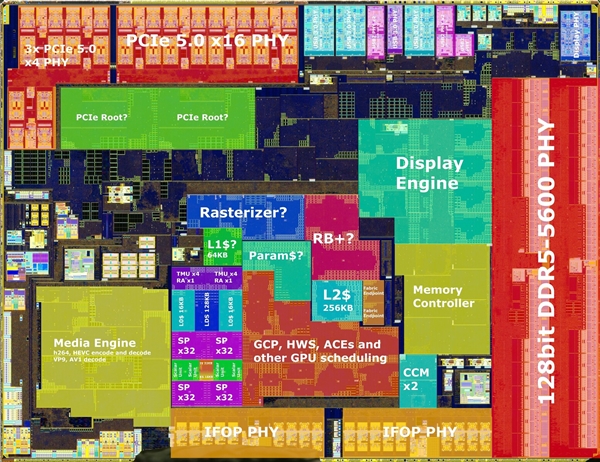

CCD整体布局如上,包括左右两排一共八个Zen5 CPU核心,夹在中间的所有核心共享的32MB三级缓存。

注意看,三级缓存的两排粉色长条区域,和以往一样,是为3D缓存预留的TSV硅通孔,锐龙9000X3D系列上会用到它。

下方是系统管理单元(SMU)、电源管理单元(PMU)、I/O互联模块,以及两个Infinity Fabric高速互连通道模块(IFoP),EPYC上它们的作用更大。

左下角紫色的区域,被标注为测试/调试之用。

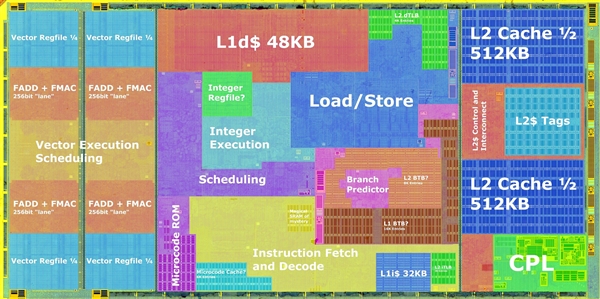

细看每个核心,左侧大片区域是矢量执行单元,主要用作浮点操作,完整支持512位浮点路径,可用于AVX-512指令,所以面积相当大,而且位于核心以及整个CCD的边缘,因为浮点运算发热量大,这样方便散热。

右侧是二级缓存,与之相连的就是三级缓存。

中间部分可以看到指令预取与解码、分支预测、微操缓存、调度器等组成的最重要的前端模块,以及32KB一级指令缓存、48KB一级数据缓存、整数执行单元、载入/存储单元。

IOD部分没啥新鲜的,128个流处理器的GPU核心、显示引擎、多媒体引擎、128-bit DDR5-5600内存控制器、28条PCIe 5.0控制器、USB 3.x/2.0控制器、两个IFoP端口。

是的,没有原生USB4,X870E/X870上的接口都来自板载第三方主控。

- 上一篇

通信能力大升级!vivo X200系列独创公里级无网通信

10月7日消息,今日,vivo品牌副总裁,兼品牌与产品战略总经理贾净东在微博上公布了vivo X200系列的相关信息。贾净东称:vivo一直是中国最核心的通信玩家之一,专注通信行业29年,多年扎根5G、6G的基础研发,不久前还获得了“国家科技进步一等奖”的隆重表彰。无论是日常“寰宇信号放大系统”的守护,让电梯内通话都可畅联、还是X100

- 下一篇

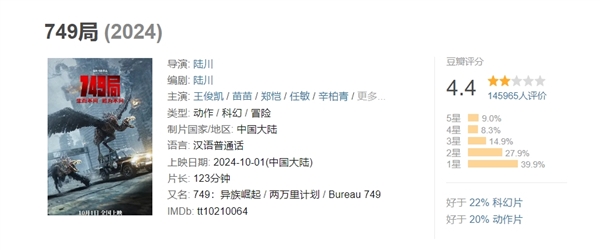

科幻冒险电影《749局》豆瓣评分降至4.4陆川回应烂片质疑:具体哪部是烂片

10月7日消息,据猫眼专业版数据,截至10月7日12时27分,2024年国庆档档期(10月1日-10月7日)票房破20亿,位列影史国庆档票房榜第6位,《志愿军:存亡之战》《749局》《浴火之路》分列国庆档票房榜前三。其中,位列票房第二的《749局》争议最大。目前,该片票房评分已降至4.4分,仅好于20%的同类影片,追平9年前《九层妖塔》个人最差口碑纪录。在145965人评价中,1星评